If I Get New Ram Do I Have to Overlcock Again

How to Overclock RAM

How To Overclock RAM

Playing the Silicon Lottery

At that place is a lot of chip-to-chip variability when it comes to memory, more than so for DDR4 than DDR3. Two identical modules, from the aforementioned manufacturing batch, may be able to take vastly different maximum voltages before condign unstable, but only in sure retentiveness slots. While vendors do test for the functioning of each IC, a memory scrap is only guaranteed to perform at the advertised specifications. The differences show upwardly when you attempt to overclock them.

Given how relatively inexpensive memory can be, serious overclockers generally purchase multiple kits, test each module, and select the all-time. The testing/selection procedure for this portion involves placing the modules (one at a fourth dimension) in the same DIMM slot with the same memory parameters, and finding the modules that run benchmarks consistently (SuperPi 32m is recommended here) with the lowest DRAM voltage possible. The modules that laissez passer with the lowest voltage are the all-time pieces of silicon.

Subsequently the best modules are selected, each is rotated into each DIMM slot on the motherboard and tested over again to find which specific module performs best in which position. This last check should be performed fifty-fifty for a configuration that is restricted to an already-purchased kit. At this point, each DIMM should be physically labeled (a sticker works well) to identify the slot information technology belongs in; keeping a log of the lowest voltages for each and the parameters used for this test is very useful if long-term damage is suspected somewhere downward the line.

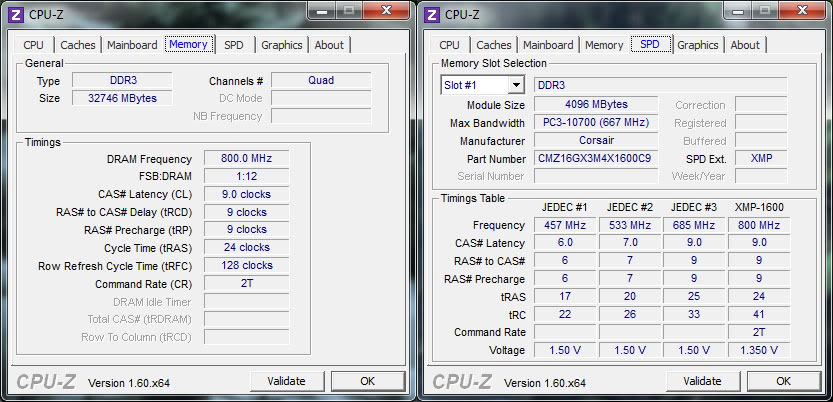

Parameters for memory overclocking can be changed via the motherboard firmware or through vendor-supplied software. Many motherboard vendors offer tuning utilities that incorporate stress testing and parameter manipulation, and there are freeware options like CPU-Z that can provide a quick system report and real-time measurement of each component's operating frequencies.

Intel offers its Farthermost Retentivity Profiles (XMP), which consist of pre-divers and validated overclocking settings that tin can exist loaded via motherboard firmware or a vendor tuning utility. XMP allows the firmware/utility to automatically configure the DRAM voltage and latencies, and it can be a good pick for those wishing to piece of work with pre-optimized variables.

For stress-testing, the customs's current favorite utility seems to be SuperPi, followed closely by Memtest86+. Both tools have extensive configuration options for running tests. Concluding benchmarking should be carried out using software that most closely mimics the application the system was intended for, similar 3DMark for graphics applications and rendering, WinRAR, virtual motorcar performance, MATLAB's memtest, etc.

Bones Overclocking

Memory overclocking, like overclocking the processor, requires iterative tuning and patience. The general procedure is:

- Confirm stability. You can use Memtest86+, SuperPi 32M, Intel's Farthermost Retentivity tool, or a motherboard/vendor supplied software suite for this.

- Note "skillful" default parameters (parameters that can be returned to if all hell breaks loose).

- Confirm (via the motherboard firmware or software suite) that the retention frequency, timings/latency, and voltage values are the ones advertised by the memory vendor. Repeat Stride 1 if any changes are fabricated.

- Set the memory multiplier to its maximum commanded value, repeat Footstep ane.

- Increase the BCLK frequency by some small corporeality (ten Hz or and then), echo Step 1. We veer abroad from optimizing the memory frequency farther if the BCLK beingness used has been set with regard to processor overclocking considerations. If the memory is unstable with the maximum memory multiplier at this point, it is ever possible to reduce BCLK, increase the CPU multiplier, or reduce the memory multiplier (or whatever combination of these parameters) to achieve system stability. You should conform the VTT in tandem with the BCLK.

- In case of problems (or just to see if it makes a difference), increase the DRAM voltage by a very small-scale increment (0.01V, for example) and repeat Step one.

- The CMD should be ready to 1 (the motherboard firmware can call this variable CR1/CR2 or T1/T2).

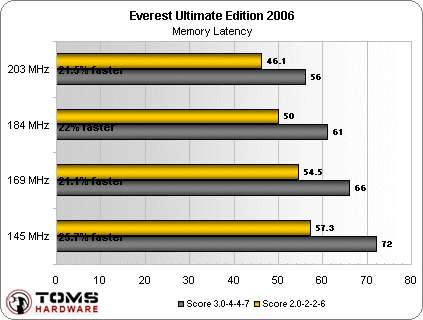

- Tighten the primary memory timings, repeat Step 1. Ideally, the timings would be tightened (decreased) for better performance, but before that it is worth loosening (increasing) them to meet if a higher BCLK or memory multiplier can be tolerated by the organization with slightly increased latencies. Tightening the memory timings begins with an adjustment of the primary timings—a benchmark/stress examination should be carried out later on each ready of changes—and proceeds in an iterative mode to lower each number in the chief timings set up. Secondary and 3rd timings have a much smaller bear upon on overall performance, simply they can exist adapted in the same manner.

Given the number of variables and infinitesimal changes that can have big effects, a stopping point for the optimization can be any of the following:

- Maximum safe DRAM voltage reached

- Maximum BCLK reached, or an incrementally higher BCLK is unstable despite all other parameters existence optimized.

- A maximum RAM frequency is reached (for DDR3; DDR4 doesn't accept a ceiling as of withal)

- The memory ICs turn down to kick considering of thermal or overvoltage damage

We tin can also go in the contrary direction. You tin can netherclock the memory for improved ability savings; lower voltage will lower power consumption a bit, although the clock rate has a far bigger affect.

RTL And IOL: Raw RAM Performance Metrics

Advanced overclocking begins with looking at the memory configuration's real latency. RTL and IOL values can exist used as fettle scores to optimize memory operation; the lower the better. Also, these figures are given in clock cycles, simply they really should be converted to real time values to get a practiced idea of the actual latency (the clock frequencies may alter).

IOL, the Input Output Latency (also referred to as I/O Latency) is the time it takes the chip to send a response after the query comes in.

RTL, the Round Trip Latency, is the length of time it takes for a signal to be sent to the memory, plus the length of time it takes for an acquittance from memory of that signal to exist received (the complete round-trip time taken for a signal to exist transmitted from point A to indicate B and so back to betoken A). RTL values are not always straight (manually) accessible, merely they are a office of the IMC frequency, tCL and clock skew (mismatch) between the IMC and DRAM clock frequency. Our sister site Anandtech extrapolated a formula for correctly predicting the RTL values. Of form, their formula requires some motherboard-specific modification, by and large based on the lath layout, specifically the altitude from the DIMM slots to the CPU.

These values may be directly accessible on some motherboards, in which case information technology makes sense to prepare them to some static "good" value to minimize instability problems, which have the potential to increase as more parameters—in addition to the BCLK/Multiplier/Master timings—are tweaked. Where the RTL initial value and IO latency Offset are manually attainable, the easiest way to tighten the RTL/IO numbers is to ready the RTL Initial Value to the everyman number that allows the memory to Postal service, then, after the organization has booted successfully, to set the IO Latency Offset value higher one bike number at a time (iteratively) until the everyman RTL/IO values are plant after a reboot.

Memory Training

There are multiple clocks in a arrangement (CPU, IMC, memory, etc.), with a variable tick/tock initialization from kickoff-up to start-up, a wide multifariousness of signal pathways and variable environmental parameters, all of which combine to create a disparity (a skew) in the real arrival fourth dimension of diverse signals at their destination. The pre-boot DDR calibration sequence introduces diverse delays betwixt signals in social club to reach synchronicity. This is where DDR training kicks in; in that location are a number of patterns (either preset/provided by vendors, or custom-made) that test diverse signal/delay sets for the all-time possible ranges of these values. The accuracy of these delays determines the RTL/IOL, and ultimately influences memory performance. Since RTLs and IOLs are fix at boot, training has a very real impact on the CAS latency.

Fast Boot settings either skip the memory training entirely, or use a very crude-and-ready form of training. While this is good enough for normal purposes, the best possible grooming sequence (determined from literature, or comparing the RTL/IOL values resulting from using each exam, or in the absence of additional data, using the sequence that takes the longest time) should be used when fine-tuning memory parameters or benchmarking, because the variable signal/delay accuracy from a sub-par training authorities makes parameter comparison questionable. Even so, if enthusiasts are looking for moderate increases in retention functioning, this step is generally optional.

Source: https://www.tomshardware.com/reviews/ram-overclocking-guide,4693-3.html

0 Response to "If I Get New Ram Do I Have to Overlcock Again"

Post a Comment